# **OMTP**

# SECURITY THREATS ON EMBEDDED CONSUMER DEVICES

| VERSION:             | v1.1                     |  |

|----------------------|--------------------------|--|

| STATUS:              | Approved for Publication |  |

| DATE OF PUBLICATION: | 28th May 2009            |  |

| OWNER:               | OMTP Limited             |  |

# **CONTENTS**

| 1        | Introduction                                                                                                                                                                                                                                       | 6            |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 1.1      | DOCUMENT PURPOSE                                                                                                                                                                                                                                   | 6            |

| 1.2      | INTENDED AUDIENCE                                                                                                                                                                                                                                  | 6            |

| 1.3      | REQUIRED EXPERTISE                                                                                                                                                                                                                                 | 7            |

| 1.4      | Ease of Repeat                                                                                                                                                                                                                                     | 7            |

| 1.5      | Ease of Distribution                                                                                                                                                                                                                               | 7            |

| 1.6      | THREATS CLASSIFICATION                                                                                                                                                                                                                             | 8            |

| 2        | THREATS SUMMARY                                                                                                                                                                                                                                    | 10           |

| 2.1      | SOFTWARE MODIFICATION THREATS (T.SWM.XXX)                                                                                                                                                                                                          | 10           |

| 2.2      | SOFTWARE OPPORTUNISTIC THREATS (T.SWO.XXX)                                                                                                                                                                                                         | 10           |

| 2.3      | HARDWARE THREATS – EXTERNAL (T.HWE.XXX)                                                                                                                                                                                                            | 12           |

| 2.4      | HARDWARE THREATS – TERMINAL INTRUSIVE (T.HWT.XXX)                                                                                                                                                                                                  | 12           |

| 2.5      | HARDWARE THREATS – COMPONENT INVASIVE (T.HWC.XXX)                                                                                                                                                                                                  | 13           |

| 2.6      | HARDWARE CLONING, COMPONENT REPLACEMENT OR COMPONENT ADDITION THREATS (T.CLO.XXX)                                                                                                                                                                  | 14           |

| 3        | TOOLS IN THE ARMOURY TO STOP THE HACKER                                                                                                                                                                                                            | 15           |

| 3.1      | PRIVILEGED CODE AND ITS ROLE IN GUARDING SECRETS                                                                                                                                                                                                   | 15           |

| 3.2      | APIs and Security                                                                                                                                                                                                                                  | 15           |

| 3.3      | Type-Safety                                                                                                                                                                                                                                        | 15           |

| 3.4      | SECURITY DOMAINS                                                                                                                                                                                                                                   | 16           |

| 3.5      | SECURITY CRITICAL ASSETS VS NON-CRITICAL ASSETS                                                                                                                                                                                                    | 16           |

| 3.6      | INTEGRITY CHECKING                                                                                                                                                                                                                                 | 17           |

| 3.7      | SECURE BOOT                                                                                                                                                                                                                                        | 19           |

| 4        | THREATS DETAILS                                                                                                                                                                                                                                    | 20           |

| 4.1      | SOFTWARE MODIFICATION THREATS (T.SWM.XXX)                                                                                                                                                                                                          | 20           |

| T.<br>T. | SWM.001 Attack via faulty privileged code extensions (e.g. drivers) SWM.002 Attack via illegal privileged code extensions (drivers) SWM.003 Unauthorised re-flash of device through FOTA SWM.004 Subverting of general software loading procedures | . 20<br>. 21 |

| 4.2      | SOFTWARE OPPORTUNISTIC THREATS (T.SWO.XXX)                                                                                                                                                                                                         | 22           |

© 2009 OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

| 7   | T.SWO.001    | Attack via faulty OS code(bug)                               | 22 |

|-----|--------------|--------------------------------------------------------------|----|

| 7   | T.SWO.002    | Attack, via unrelated application APIs, to secure resources. | 23 |

|     |              | Breaking Access Control performed by software to hardware    |    |

|     | eatures      | •                                                            | 24 |

|     |              | Breaking Access Control performed by software to             |    |

|     |              | ·                                                            | 24 |

|     |              | Buffer overflows                                             |    |

|     |              |                                                              |    |

|     |              | Code verifiability related security holes                    |    |

|     |              | Unpredictable CPU instructions                               |    |

|     |              | B DMA or CLCD use for accessing memories                     |    |

|     |              | Faking of general software identity                          | 27 |

| 7   | T.SWO.010    | CLCD use for displaying memories and interfering with        |    |

| C   | displayed da | ata                                                          | 28 |

| 7   | T.SWO.011    | Attack through uncontrolled API in general software space.   | 28 |

|     |              | Attack through uncontrolled instruction set space            |    |

|     |              | Attack through interaction of software concurrent processes  |    |

|     |              | ·                                                            | 29 |

|     |              | Exploit software bugs in execution environment               |    |

|     |              | Software Attack on Type Unsafe APIs inside the execution     | 00 |

|     | environmen   |                                                              | 30 |

| _   |              |                                                              | 30 |

|     |              | Software Attack on Type-Safe APIs inside the Execution       | 20 |

|     | Environmen   |                                                              |    |

| ı   | 1.SWO.017    | ' Attack Through Virtual Debug Port                          | 31 |

| 4.3 | B HARDW      | vare Threats – External (T.HWE.xxx)                          | 31 |

| _   |              | ,                                                            |    |

|     |              | Unauthorised access via external invasive or non-invasive    |    |

|     | • .          | (                                                            | 31 |

|     |              | ! Unauthorised re-Flash of device through external debug por | rt |

| (   | e.g. JTAG)   |                                                              | 32 |

| 7   | T.HWE.003    | Unauthorised re-flash of device through external serial      |    |

| İ   | nterface     |                                                              | 32 |

| 7   | T.HWE.004    | Bypass security by external battery removal                  | 33 |

|     |              | Bypass security by external memory card removal              |    |

|     |              | Scan chain attack (direct or side channel)                   |    |

|     |              | Built-in self-test                                           |    |

| •   |              |                                                              |    |

| 4.4 | HARDW        | vare Threats – Terminal Intrusive (T.HWT.xxx) 3              | 34 |

| -   | T 1111/T 001 | Extract secret via Rus monitoring (hardware probes)          | 21 |

|     |              | Extract secret via Bus monitoring (hardware probes)          |    |

|     |              | Unauthorised access via internal but off-SOC invasive or no  |    |

|     |              | bug Ports (e.g. JTAG, ETM)                                   | 35 |

|     |              | General hardware Attack on data in external RAM (e.g.        |    |

|     |              |                                                              |    |

|     |              | Hardware Attacks on static information in internal RAM (on-  |    |

|     |              | de package)                                                  |    |

| 7   | T.HWT.005    | Power analysis Attack to reveal secrets                      | 36 |

|     |              | Time analysis Attack to reveal secrets                       |    |

|     |              | Bypass security by glitch Attacks (e.g. power)               |    |

|     |              |                                                              |    |

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

|   | <b>T.HWT.008</b> Bypass security by power removal to NV memory                                                                                                           | es           |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 4 | .5 HARDWARE THREATS – COMPONENT INVASIVE (T.HWC.XXX)                                                                                                                     |              |

|   | T.HWC.001 Extract secret via Bus monitoring (de-cap/drill & hardware probes)                                                                                             | . 39         |

|   | T.HWC.002 Hardware Attacks on static information in internal RAM (on SoC, inside IC package)                                                                             | . 40<br>. 40 |

|   | T.HWC.005 Focused Ion Beam (FIB) manipulation T.HWC.006 Probe Stations                                                                                                   | . 41         |

| 4 | .6 HARDWARE CLONING, COMPONENT REPLACEMENT OR COMPONENT ADDITION THREATS (T.CLO.XXX)                                                                                     | 42           |

|   | T.CLO.001 Cloning Device by copying PCB and Flash T.CLO.002 External RAM Chip Replacement Attack T.CLO.003 Hardware Attacks to change static information in external RAM | . 43         |

|   | T.CLO.004 Hardware Attacks to change dynamic information in externa                                                                                                      | _            |

|   | T.CLO.005 Attack by replacement of Flash when power is off (pre-boot,                                                                                                    | )            |

|   | T.CLO.006 Attack by replacement of Flash when power is on (post-boo                                                                                                      | t)           |

| 5 | DEFINITION OF TERMS                                                                                                                                                      |              |

| 6 | ABBREVIATIONS                                                                                                                                                            | 48           |

| 7 | REFERENCED DOCUMENTS                                                                                                                                                     | 50           |

The information contained in this document represents the current view held by OMTP Limited on the issues discussed as of the date of publication.

This document is provided "as is" with no warranties whatsoever including any warranty of merchantability, non-infringement, or fitness for any particular purpose. All liability (including liability for infringement of any property rights) relating to the use of information in this document is disclaimed. No license, express or implied, to any intellectual property rights are granted herein.

This document is distributed for informational purposes only and is subject to change without notice. Readers should not design products based solely on this document.

Each Open Mobile Terminal Platform member and participant has agreed to use reasonable endeavours to inform the Open Mobile Terminal Platform in a timely manner of Essential IPR as it becomes aware that the Essential IPR is related to the prepared or published specification. The declared Essential IPR is publicly available to members and participants of the Open Mobile Terminal Platform and may be found on the "OMTP IPR Declarations" list at the OMTP Members Access Area.

The Open Mobile Terminal Platform has not conducted an independent IPR review of this document and the information contained herein, and makes no representations or warranties regarding third party IPR, including without limitation patents, copyrights or trade secret rights. This document may contain inventions for which you must obtain licenses from third parties before making, using or selling the inventions.

Defined terms and applicable rules above are set forth in the Schedule to the Open Mobile Terminal Platform Member and Participation Annex Form.

© 2009 Open Mobile Terminal Platform Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited. "OMTP" is a registered trademark. Other product or company names mentioned herein may be the trademarks of their respective owners.

OM TP OPEN MOBILE TERMINAL

Page 5 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

#### 1 Introduction

#### 1.1 DOCUMENT PURPOSE

When defining the Security Policy of a User Equipment (UE, as defined in 3GPP TR 21.905 [1]), the relevance of each of the Threats applicable to UE Assets should be taken into consideration. Indeed, protecting specific Assets against specific Threats must be considered as a balance of cost of security protection vs. cost of security break.

Cost of security protection encompasses:

- Increased development time

- Increased silicon cost

- Increased manufacturing and test time, including:

- Installing the security

- Verifying the security

- Increased device complexity

- Decreased device performance

Cost of security break includes:

- · Potential cost of the device

- Service and support in countering the break

- The cost can be in reputation or pure financial terms and can affect

- The manufacturer

- The software provider

- The information owner

- The information user

- The operator

This document defines a list of common Threats that may apply to a UE. The potential danger of each Threat, as well as the ease of creation, spreading, and blocking of each Threat is also described.

#### 1.2 INTENDED AUDIENCE

This document is written for those who have an understanding of security and require details of possible Threats applicable to UEs.

Page 6 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

## 1.3 REQUIRED EXPERTISE

The level of required expertise reflects the expertise of a Threat Agent and the availability of tools required to find a vulnerability that can be exploited.

| Easy     | Can be implemented by a UE user                                         |

|----------|-------------------------------------------------------------------------|

| Moderate | Requires expert knowledge to perform                                    |

| Hard     | Requires expert knowledge and expensive laboratory resources to perform |

#### 1.4 EASE OF REPEAT

The ease of repeat reflects the expertise, cost and time to reproduce the Attack on UEs other than the device where the vulnerability was originally found.

| Easy     | Can be repeated by UE user                                             |

|----------|------------------------------------------------------------------------|

| Moderate | Can be repeated by backstreet shop                                     |

| Hard     | Requires expert knowledge and expensive laboratory resources to repeat |

#### 1.5 EASE OF DISTRIBUTION

The ease of distribution reflects how easy it is to spread the result of the Attack, or to distribute methodology in order to reproduce the Attack.

| www                | Information can be spread on the World Wide Web once the first break is accomplished, typically distributed as software to repeat the exploit or as the discovered secret. |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | This can be considered indicative of the worst case.                                                                                                                       |

| Small<br>Corporate | Requires a small corporation to make use of information / distribute the security crack, e.g. to manufacture modification chips, called hereafter "Mod Chips"              |

| Corporate          | Requires a large corporation to make use of the information, e.g. to create and sell cloned phones                                                                         |

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 7 of 50 OMTP PUBLISHED

Some Attacks directly create a result, such as running a piece of software that allows a device to ignore DRM when played on that device.

OPEN MOBILE TERMINAL PLATFORM

Some Attacks result in a piece of data that can then be used elsewhere. For example, a piece of software that runs on a device and sends the owner's credit card details (the result) back to a thief for future use.

Any Attack that reveals a class secret (such as the credit card details above) is immediately considered "WWW" distributable (synonymous with the worst case).

#### 1.6 THREATS CLASSIFICATION

While it is possible to divide Threats into a number of classifications and to varying degrees of granularity, this document divides Threats into six categories to enable intuitive understanding of the Threat (with associated Required Expertise, Ease of Repeat and Ease of Distribution) as well as to keep the number of categories to a minimum in order to maintain simplicity within the document.

The six categories of Threats and their definitions are listed below

- 1. Software Modification Threats (T.SWM.xxx)

- Logical Threats aiming to modify the software of the UE.

- 2. Software Opportunistic Threats (T.SWO.xxx)

- Logical Threats aiming to take advantage of a weakness in either the definition or implementation of the software in the UE. The Threat could expose secrets or cause the terminal to behave in an unintended or unauthorised way.

- 3. Hardware Threats External (T.HWE.xxx)

- Physical Threats which can be implemented without any breach of the terminal's Integrity, generally through the ports and connectors available outside of the UE.

- 4. Hardware Threats Terminal Intrusive (T.HWT.xxx)

- Physical Threats which are implemented by opening the outer encasing of the UE. These include probing of busses on the PCB or the exposed pins of a package mounted on the PCB. This includes the physical removal of a component for offline Attacks if the component's Integrity is not physically damaged in the removal process or the Attack.

- 5. Hardware Threats Component Invasive (T.HWC.xxx)

- Physical Threats or Attacks which are implemented by affecting the physical Integrity of the component (breach or destruction), including but not limited to the SoC, Memories, and PCB. This includes the physical removal of a component for offline Attacks if the component's

Page 8 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Integrity is physically damaged in the removal process or the Attack.

- 6. Hardware Cloning, Component Replacement or Component Addition Threats (T.CLO.xxx)

- Physical Threats which consist of replacing a part or the entire UE with an alternative component, or of adding a component to the UE. This includes but is not limited to replacing the SoC or Memory with another SoC or Memory as well as creating a copy of the UE.

Page 9 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

# **2 THREATS SUMMARY**

# 2.1 SOFTWARE MODIFICATION THREATS (T.SWM.XXX)

| THREAT DESCRIPTION                                                           | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| <b>T.SWM.001</b> Attack via faulty privileged code extensions (e.g. drivers) | Moderate              | Easy              | WWW                     |

| T.SWM.002 Attack via illegal privileged code extensions (drivers)            | Moderate              | Easy              | www                     |

| T.SWM.003 Unauthorised re-<br>flash of device through FOTA                   | Hard                  | Hard              | Small Corp              |

| T.SWM.004 Subverting of general software loading procedures                  | Moderate              | Moderate          | WWW                     |

# 2.2 SOFTWARE OPPORTUNISTIC THREATS (T.SWO.XXX)

| THREAT DESCRIPTION                                                                                | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|---------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| T.SWO.001 Attack via faulty OS code(bug)                                                          | Moderate              | Easy              | www                     |

| <b>T.SWO.002</b> Attack, via unrelated application APIs, to secure resources                      | Moderate              | Easy              | WWW                     |

| T.SWO.003 Breaking Access<br>Control performed by software to<br>hardware features                | Moderate              | Easy              | www                     |

| T.SWO.004 Breaking Access<br>Control performed by software to<br>confidential data, code and keys | Moderate              | Easy              | www                     |

| T.SWO.005 Buffer overflows                                                                        | Moderate              | Easy              | www                     |

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 10 of 50 OMTP PUBLISHED

| THREAT DESCRIPTION                                                                           | REQUIRED EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|----------------------------------------------------------------------------------------------|--------------------|-------------------|-------------------------|

| T.SWO.006 Code verifiability related security holes                                          | Moderate           | Easy              | WWW                     |

| T.SWO.007 Unpredictable CPU instructions                                                     | Hard               | Easy              | WWW                     |

| <b>T.SWO.008</b> DMA or CLCD use for accessing memories                                      | Moderate           | Easy              | WWW                     |

| <b>T.SWO.009</b> Faking of general software identity                                         | Moderate           | Easy              | WWW                     |

| T.SWO.010 CLCD use for displaying memories and interfering with displayed data               | Moderate           | Easy              | www                     |

| T.SWO.011 Attack through uncontrolled API in general software space                          | Moderate           | Easy              | WWW                     |

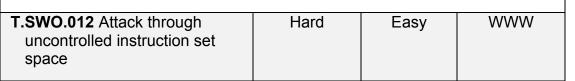

| T.SWO.012 Attack through uncontrolled instruction set space                                  | Hard               | Easy              | WWW                     |

| T.SWO.013 Attack through interaction of software concurrent processes causing logical breaks | Hard               | Moderate          | WWW                     |

| T.SWO.014 Exploit software bugs in execution environment                                     | Moderate           | Easy              | www                     |

| T.SWO.015 Software Attack on Type Unsafe APIs inside the execution environment               | Moderate           | Easy              | WWW                     |

| T.SWO.016 Software Attack on<br>Type-Safe APIs inside the<br>execution environment           | Hard               | Easy              | www                     |

| T.SWO.017 Attack Through virtual debug port                                                  | Moderate           | Easy              | WWW                     |

<sup>©</sup> 2009 OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

# 2.3 HARDWARE THREATS - EXTERNAL (T.HWE.XXX)

| THREAT DESCRIPTION                                                                               | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|--------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| T.HWE.001 Unauthorised access via external invasive or non-invasive debug ports (e.g. JTAG, ETM) | Moderate              | Moderate          | Small Corp              |

| T.HWE.002 Unauthorised re-<br>flash of device through external<br>debug port (e.g. JTAG)         | Moderate              | Moderate          | Small Corp              |

| T.HWE.003 Unauthorised re-<br>flash of device through external<br>serial interface               | Moderate              | Easy              | Small Corp              |

| T.HWE.004 Bypass security by external battery removal                                            | Easy                  | Easy              | WWW                     |

| T.HWE.005 Bypass security by external memory card removal                                        | Easy                  | Easy              | www                     |

| T.HWE.006 Scan chain attack (direct or side channel)                                             | Moderate              | Moderate          | Small Corp              |

| T.HWE.007 Built-in self-test                                                                     | Moderate              | Moderate          | Small Corp              |

# 2.4 HARDWARE THREATS - TERMINAL INTRUSIVE (T.HWT.XXX)

| THREAT DESCRIPTION                                                                                                  | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|---------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| <b>T.HWT.001</b> Extract secret via Bus monitoring (hardware probes)                                                | Moderate              | Moderate          | Small Corp              |

| <b>T.HWT.002</b> Unauthorised access via internal but off-SoC invasive or non-invasive debug ports (e.g. JTAG, ETM) | Moderate              | Moderate          | Small Corp              |

| T.HWT.003 General hardware<br>Attack on data in external RAM<br>(e.g. probing)                                      | Hard                  | Moderate          | Small Corp              |

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 12 of 50 OMTP PUBLISHED

| THREAT DESCRIPTION                                                                                    | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|-------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| <b>T.HWT.004</b> Hardware Attacks on dynamic information in internal RAM (on-SoC, outside IC package) | Hard                  | Hard              | Small Corp              |

| T.HWT.005 Power analysis Attack to reveal secrets                                                     | Hard                  | Hard              | WWW                     |

| <b>T.HWT.006</b> Time analysis Attack to reveal secrets                                               | Hard                  | Hard              | www                     |

| <b>T.HWT.007</b> Bypass security by glitch Attacks (e.g. power)                                       | Hard                  | Hard              | www                     |

| T.HWT.008 Bypass security by power removal to NV memory                                               | Moderate              | Moderate          | www                     |

| T.HWT.009 Attack through interaction of hardware concurrent processes causing logical breaks          | Hard                  | Moderate          | www                     |

# 2.5 HARDWARE THREATS - COMPONENT INVASIVE (T.HWC.XXX)

| THREAT DESCRIPTION                                                                                     | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|--------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| T.HWC.001 Extract secret via<br>Bus monitoring (de-cap/drill &<br>hardware probes)                     | Hard                  | Hard              | Small Corp              |

| T.HWC.002 Hardware Attacks on static information in internal RAM (on-SoC, inside IC package)           | Hard                  | Hard              | Small Corp              |

| T.HWC.003 Hardware Attacks on<br>dynamic information in internal<br>RAM (on-SoC, inside IC<br>package) | Hard                  | Hard              | Small Corp              |

| T.HWC.004 De-capping of the chip holding secrets                                                       | Hard                  | Hard              | Small Corp              |

Page 13 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

| THREAT DESCRIPTION                            | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|-----------------------------------------------|-----------------------|-------------------|-------------------------|

| T.HWC.005 Focused Ion Beam (FIB) manipulation | Hard                  | Hard              | Small Corp              |

| T.HWC.006 Probe stations                      | Hard                  | Hard              | Small Corp              |

# 2.6 HARDWARE CLONING, COMPONENT REPLACEMENT OR COMPONENT ADDITION THREATS (T.CLO.XXX)

| THREAT DESCRIPTION                                                       | REQUIRED<br>EXPERTISE | EASE OF<br>REPEAT | EASE OF<br>DISTRIBUTION |

|--------------------------------------------------------------------------|-----------------------|-------------------|-------------------------|

| T.CLO.001 Cloning device by copying PCB and Flash                        | Hard                  | Hard              | Corporate               |

| T.CLO.002 External RAM Chip Replacement Attack                           | Hard                  | Moderate          | Small Corp              |

| T.CLO.003 Hardware Attacks to change static information in external RAM  | Hard                  | Moderate          | Small Corp              |

| T.CLO.004 Hardware Attacks to change dynamic information in external RAM | Hard                  | Moderate          | Small Corp              |

| T.CLO.005 Attack by replacement of Flash when power is off (pre-boot)    | Hard                  | Moderate          | Small Corp              |

| T.CLO.006 Attack by replacement of Flash when power is on (post-boot)    | Hard                  | Moderate          | Small Corp              |

Page 14 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

# 3 TOOLS IN THE ARMOURY TO STOP THE HACKER

The information that follows covers a number of areas that should be considered in any security conscious system design.

#### 3.1 Privileged Code and its Role in Guarding Secrets

Many Threat descriptions contain a reference to unauthorised code privilege escalation into kernel mode.

Operating systems typically use a memory management unit (MMU) in the CPU to enforce code and data isolation and hence provide security to a set of features in the operating system. This isolation is controlled by code running in privileged mode.

Unfortunately, as well as the MMU control code, other code also runs in privileged mode and there are typically many ways of entering privileged mode. Once any rogue code is able to execute in the privileged state it is much easier for it to extract secrets or modify any security functionality in a system. Therefore, breaking into privileged mode is a key initial goal of many security cracks.

## 3.2 APIS AND SECURITY

Code uses APIs to communicate between one task and another. Many Attacks are focused on misuse of APIs, either to cause the APIs to provide information they are not meant to expose, or to cause the code on the other side of the API to perform illegal actions.

In general, APIs are another key area of Attack, and are one of the routes to break into privileged mode.

One reason that APIs are often vulnerable is that they are designed with goals other than security in mind. Typically speed and functionality are the primary drivers for general API development.

A typical OS may have hundreds or thousands of APIs across the user/privileged boundary, many of which cannot be 'secured' as this will break legacy code.

#### 3.3 TYPE-SAFETY

Type describes the sort of data a block of memory holds.

This description may specify the following:

- That a particular data element is a string or an integer or a floating point etc.

- How many bytes of memory it resides in

- The value range it may occupy (1 to 5, Monday to Friday etc)

© 2009 OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 15 of 50 OMTP PUBLISHED

Fundamentally, data in a Type-Safe API is strongly checked to make sure it is what it claims to be, and often contains information related to more than one of the above 3 points attached directly to each block of data.

OM TP OPEN MOBILE TERMINAL PLATFORM

Typical APIs are not written to be Type Safe, as there is an overhead to be paid in terms of performance and flexibility to perform this checking.

If an API set between user and privileged space is Type-Safe then that gives strong assurance that that interface will not leak data through API misuse (it may still leak through logic flaws in the code behind the API). However, if there is both a Type-Safe API between user and privileged mode, and a non-Type-Safe API covering a different set of functionality, then the Type-Safe API is vulnerable to flaws in the non-Type-Safe API (e.g. a buffer Overflow Attack breaking the privileged /user boundary).

#### 3.4 SECURITY DOMAINS

Security domains are areas of code or memory, either logically or physically separate from the general software domain of a general OS. These area(s) contain code and data of specific security interest.

Unfortunately, the term domain is used for a number of purposes – even within the security industry. To prevent confusion, this document refers to the secure world and normal (or non-secure) world, rather than secure or non-secure domains.

## 3.5 SECURITY CRITICAL ASSETS VS NON-CRITICAL ASSETS

Throughout this document, a general OS is discussed as a source of many potential Threats. This is because in a typical embedded environment there are two goals from the platform point of view:

- 1. Provide a rich user experience with versatile connectivity to different external information sources

- 2. Keep secrets on the platform safe from extraction

Separation of these two goals has advantages, at least in clarity of objectives. Take as an example a device with secure connection over TCP/IP:

- On the device there may be a TCP/IP stack to provide Internet connectivity

- It may also require HTTPS to establish a secure connection

- HTTPS sits on top of TCP/IP

- TCP/IP internals do not have to be secure, as those same internals will be duplicated on numerous routing servers between the device and, for example, a bank

- Security software only has to worry about placing the HTTPS protocol on top of TCP/IP, and would actually be harmed by the inclusion of the TCP/IP stack in its 'domain' due to the dangers

Page 16 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

of code bloat and the need for verification of this code before release

This leads to considering a device as containing a general OS with the entire rich user interface, peripheral connectivity and protocol provision services, and a separate domain containing the security critical code and data segments.

Why consider this separation?

- The number of potential flaws in security can be directly linked to code size

- One boundary used for two tasks, security and "other operations", is flawed from the security point of view by exploitable flaws in those "other operations"

- Change of code behind a security boundary should be kept to a minimum. It should be separable from a general system re-build

If security tasks can be separated from general tasks then the critical code size and other vulnerabilities can be reduced, and as a bonus extra precautions can be taken that couldn't be applied to the general code (e.g. relocate code to a physically safer space)

#### 3.6 INTEGRITY CHECKING

One solution to the problem of "hacks" modifying a system is to perform Integrity checking on the current system code and data.

This requires three things:

- knowledge of the correct state of that system code and data;

- a trustable entity that verifies that the system code and data is in a correct state":

- an effective and non-circumventable response to an integrity failure.

One way to perform integrity checking is to calculate a signature value over a block of data and compare that value to a reference value. Data and code can be checked by software, running in a more trusted space, or by hardware. The time to perform those checks can be considerable.

#### For instance:

A typical hashing algorithm takes around 22 Cycles per byte.

On a 200MHz CPU that gives

0.22 Seconds to check an entire 2Mb RTOS

Page 17 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

#### 2.2 Seconds to check an entire 20Mb smartphone OS

This speed restriction may raise problems in a system design.

Integrity checking works best where information is in a relatively static environment.

If some other task is moving the information around then the Integrity checker has to be informed (and trust that other task to be doing legal movements).

If the data is dynamic then the Integrity checker has to modify its reference values each time that data is changed (and trust the changer was performing a legal action).

#### Suggested Solutions:

- Consider how often such a check must occur:

- For Integrity failures that lead to instantaneous loss of a valuable resource, any instance of a security break is critical

- For Integrity failures that have long term consequences on a device, (e.g. IMEI modification on phones) then it may be acceptable to test the Integrity over a period of days or weeks.

- If the memory cannot be attacked after it is loaded, then that validation check only has to be done on load.

- This is why Secure Boot is so critical.

- Consider if everything needs to be checked:

- If software is placed behind a security boundary that is safe from all considered Threats, then it does not need to be checked once it has been put in place

- Security software may require a TCP/IP stack to transmit its secrets to remote devices – but that security software will be running safeguards on top of the TCP/IP to prevent interception of data (e.g. HTTPS), so the TCP/IP stack itself may not have to be checked for breaks

- Similar arguments can be considered for much of the graphical and I/O environment of a device

- In a typical general OS, the kernel and Access Control software are only a few hundred kilobytes. If that is verified then that may be sufficient re-assurance

- Consider who does the checking

- If Integrity is validated in one part of a device, then that part can act as the gatekeeper to other functionality

- Such Integrity can be built in a tree of trust, with one part offering validation to another, as long as the susceptibility

OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

to Attack of that one part is considered lower than that which it is validating

#### 3.7 SECURE BOOT

Trust in a system is built up from a well known defined point, known as the "root of trust". Typically, this might be an on-chip key, which can be used to verify code and data brought in from elsewhere in the system. Where that root of trust is used to validate the operating environment for the Execution Environment, the process is known as Secure Boot, and establishes that:

- The system booted a valid OS or Virtual Machine Monitor (VMM)

- The system loaded valid drivers and kernel modules

- The system loaded valid applications

By "valid" it means that the code and static data being loaded is that which is expected by the secure boot authority.

If the Secure Boot process completes correctly, there is an assurance that the booted execution environment is one that the Secure Boot authority (e.g. device manufacturer or network operator) approved.

Page 19 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

# 4 THREATS DETAILS

The following list of Threats is not comprehensive but should act as a starting point when considering a system design.

Each Threat comes with a description of the Threat and a list of suggested solutions that may or may not be appropriate on a particular device.

# 4.1 SOFTWARE MODIFICATION THREATS (T.SWM.XXX)

| THREAT DESCRIPTION                                                           | REQUIRED  | EASE OF | EASE OF      |

|------------------------------------------------------------------------------|-----------|---------|--------------|

|                                                                              | EXPERTISE | REPEAT  | DISTRIBUTION |

| <b>T.SWM.001</b> Attack via faulty privileged code extensions (e.g. drivers) | Moderate  | Easy    | WWW          |

#### Description:

This form of Attack occurs when a typical OS is forced to allow changes to privileged code due to the need to enable changing of driver software. Driver software in such an OS typically has privileged access to handle interrupts from peripherals.

One problem in this area is that drivers are typically written by third parties and drivers are upgraded at different times to the main OS. This causes problems when implementing any "whole device" validation scheme, or even isolated checking of specific software updates

This code has a relatively high turnover for privileged code, is not written with a security focus, and therefore is vulnerable to a higher incidence of security flaws.

## **Suggested Solutions:**

- Prevent downloading of privileged code

- Introduce a scheme of privileged code signing and certification

- Reduce size of privileged code using VMM or user-mode drivers techniques

Introduce another level of security safe from privileged access

| T.SWM.002 Attack via illegal | Moderate | Easy | WWW |

|------------------------------|----------|------|-----|

| privileged code extensions   |          |      |     |

| (drivers)                    |          |      |     |

|                              |          |      |     |

#### Description:

This form of Attack occurs because a typical OS is forced to allow changes to Privileged code through changes to driver software. Driver software in such an OS has privileged access if it is not running on top of a VMM.

Threat Agents intentionally write software to appear as a drivers to the OS,

Page 20 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

thus enabling the exploitation of this access loophole.

# **Suggested Solutions:**

- Prevent unauthorised downloading of privileged code

- Only permit download from trusted sources

- Only permit download when activated by an authorised route

- Prevent downloading of privileged code

- Introduce a scheme of privileged code signing and certification

- Reduce size of privileged code using VMM, user-mode drivers techniques

- Introduce another level of security safe from privileged access

| T.SWM.003 Unauthorised re-   | Hard | Hard | Small Corp |

|------------------------------|------|------|------------|

| flash of device through FOTA |      |      |            |

#### Description:

FOTA (Firmware Over The Air) has to be considered separately from the general execution environment of a device, as it often works as part of the boot sequence, replacing one version of the general OS(s) with another.

The Threat is in the use of this valid update technique with invalid data.

This is the sort of Attack that may occur as soon the current range of more direct re-flashing Attacks is stopped. It requires the update server's message to be faked at some point in its life cycle, or to place a FOTA update package on the device through other methods.

This is a particularly nasty Attack if a device is vulnerable to it, in that it can completely change a device, perhaps without the user being aware that this is happening, and it can almost certainly be done remotely.

#### Suggested solutions:

- Make sure that only validated and signed data is used to re-flash the device

- Consideration must then be given as to where to store the validating and signature check code and data, and what the fallback position is if the current set of keys is leaked

- Make sure that only validated and signed code can be executed on the device as a result of re-flashing

Note: Current FOTA solutions claim this capability, and it may be considered that as they execute during a device re-boot, that their keys and software are validated and no opportunity to Attack them exists. It may be that only hardware Attacks can break current FOTA solutions, in which case why would a user allow their device to be so vulnerable, however many current Threats appear as Trojans and it may be in the future that such Trojan

OPEN MOBILE TERMINAL PLATFORM

Page 21 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

hardware modifications exist e.g. "This Mod Chip gives you free DRM (by breaking FOTA security)".

| T.SWM.004 Subverting of  | Moderate | Moderate | WWW |

|--------------------------|----------|----------|-----|

| general software loading |          |          |     |

| procedures               |          |          |     |

# Description:

One place that the general OS may perform Integrity and Access Control checks is in the OS file loader. In this context, the file loader is the piece of code that allocates memory and then loads code from long term storage (Flash, hard drive etc) for execution as an executable, dynamically linked library or even driver. It may also inform the rest of the system as to the rights of that piece of code when it comes to dealing with APIs.

Therefore the file loader is a particularly critical piece of security code and if replaced with non-checking, full-access granting code, this would bypass much of any OS security.

By its very nature the file loader can often be considered a static piece of code (as nothing exists to move it around), hence its placement in memory can be carried out through secure boot.

Typically this means that it can only be Attacked by breaks in the user/privileged code split or through hardware techniques, allowing the file loader or information it is dependent upon to be replaced, or modified.

#### Suggested Solutions:

- Move this piece of code behind another layer of security boundary

- Perform checks to ensure that no code and static changes have been made to this piece of code

- If the file loader is outside the general security infrastructure (for performance reasons), perform remote load requests from the secure code base to see if the file loader security is running as expected

# 4.2 SOFTWARE OPPORTUNISTIC THREATS (T.SWO.XXX)

| THREAT DESCRIPTION                       | REQUIRED  | EASE OF | EASE OF      |

|------------------------------------------|-----------|---------|--------------|

|                                          | EXPERTISE | REPEAT  | DISTRIBUTION |

| T.SWO.001 Attack via faulty OS code(bug) | Moderate  | Easy    | WWW          |

#### Description:

Recent studies have shown up to 33 security specific flaws per million lines of average code. (A long term study of the OpenBSD code base [2]).

Page 22 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Typical C code produces 17 bytes per line [3].

So for a typical 20Mb Feature phone there may be 40 security flaws.

This is not including bugs that just crash the system; these 40 are specifically security related flaws that leak secrets, break Access Control or the like.

# **Suggested Solutions:**

- Reduce code size

- Intensify testing and reviewing on security critical code

- · Isolate security critical code from general code base

| T.SWO.002 Attack, via unrelated | Moderate | Easy | WWW |

|---------------------------------|----------|------|-----|

| application APIs, to secure     |          |      |     |

| resources.                      |          |      |     |

|                                 |          |      |     |

#### **Description:**

Each and every API in an OS can potentially expose security vulnerabilities, even if it has nothing to do with security. This is because the OS APIs are the OS's separation mechanism between different domains of privileged data. That privileged data may be related to secrets, it may be related to methods of drawing on the screen, or it may be related to allocating memory and manipulating the MMU. Unfortunately these APIs are critical to exposing the rich and versatile functionality that general OS's need to provide. Adding security to all APIs slows down the OS and requires the re-writing of large areas of affected code.

# Example of API vulnerabilities:

- OpenFile("C:\test.txt") is a legal API being used legally

- OpenFile("DBG:") is using that legitimate API, but making use of potential errors deeper down in the OS structure

- OpenFile("http://127.0.0.1/config.asp -SimUnlock") is using that legitimate API, but making use of potential errors deeper down in the OS structure

- OpenFile("%c%c") might cause an OS to report an error in the filename, but the error reporting code may break when displaying %c%c and display critical stack data. (%c is an internal command to the 'C' print instruction to display information that is on the stack)

## Suggested Solutions:

- Use Type-Safe APIs so malformed data cannot be sent through them

- Isolate security critical code from the general code base, so that the boundary that must be crossed to enter that code is not the same one as that being crossed by general code API usage (e.g. the security

© 2009 OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 23 of 50 OMTP PUBLISHED

code is not in the same domain or sub-domain group as the graphics driver code)

| T.SWO.003 Breaking Access     | Moderate | Easy | WWW |

|-------------------------------|----------|------|-----|

| Control performed by software |          | -    |     |

| to hardware features          |          |      |     |

| 10 11011 0111 011 0 10 011011 |          |      |     |

### Description:

This is a sub-category of T.SWM.001 or T.SWO002 in which there is a flaw in an API. In this case the Attack is on an API that allows the Threat Agent to access hardware.

This often leads to further vulnerabilities as hardware has different access rights to software.

This vulnerability is increased in an environment where the APIs are forced to follow a schema created for a more general interface need. For example, general operating systems do not use Type-Safe structures to pass data across APIs because of the speed overhead, whereas a security specific API should ideally be using such structures

### Suggested Solutions:

- Place critical hardware Access Control software in environment separated from general code base

- Consider if hardware (such as DMAs or CLCD controllers) can be used to circumvent other security (see T.SWO.008)

- Lock down some hardware capabilities so that they cannot be changed at the wrong 'time', e.g. system resources should only be allocated during boot

- A good quality secure boot and system design should enable this

- Provide hardware and/or additional software features that restrict circumvented Access Control from exposing secrets

- Reduce size of security code to reduce incidence of bugs

- Perform detailed code analysis

| T.SWO.004 Breaking Access      | Moderate | Easy | WWW |

|--------------------------------|----------|------|-----|

| Control performed by software  |          |      |     |

| to confidential data, code and |          |      |     |

| keys                           |          |      |     |

#### Description:

This is a sub-category of T.SWM.001 or T.SWO002 in which a flaw in a security API allows the Threat Agent to access software or data. This

Page 24 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

vulnerability is increased in an environment where the APIs are forced to follow schema created for a more general interface need.

For example, general OS's do not use Type-Safe structures to pass data across APIs because of the speed overhead, whereas a security specific API should ideally be using such structures.

# Suggested solutions:

- Deploy Type-Safe APIs across vulnerable boundaries to ease good practice

- Do not mix Type-Safe and non-Type-Safe APIs across the same API domain boundary

- Reduce the size of security code to reduce incidence of bugs

- Perform detailed code analysis

| T.SWO.005 Buffer overflows | Moderate | Easy | WWW |

|----------------------------|----------|------|-----|

|                            |          |      |     |

#### Description:

This can be classified as the classic example of the vulnerability exposed through use of non-Type-Safe APIs (See T.SWO.004).

By passing data through an API where it is known that the API is designed to receive X bytes and we are passing X+N bytes, it can be arranged that the N bytes overflow into an area that was used by other storage (if it is a heap overflow) or will cause the return address to be corrupted (if it is a stack overflow).

Stack overflow allows the "Return" instructions (at the end of each block of code) to jump to random locations and therefore illegally run random code, or local data to be changed – for example modifying the local rights of a piece of code.

Heap overflow can allow injection of different data into other areas of the OS, and hence allow security control information to be modified.

#### Suggested solutions:

- Use a Type-Safe API; where all data has specified size information Buffer Overflow is prevented by buffer size tracking. Such tracking has a notable speed overhead.

- As above but only apply this to the boundary into security critical software

- Note: it is of no value having a Type-Safe API across a domain boundary, if elsewhere there is a non-Type-Safe API across the same boundary, it will then be the non-Type-Safe boundary that

Page 25 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

| is being attacked, not the particular API functionality. |          |      |     |

|----------------------------------------------------------|----------|------|-----|

| T.SWO.006 Code verifiability related security holes      | Moderate | Easy | WWW |

Bugs and security flaws exist in code, but it is possible to mitigate their occurrence. It is known that these bugs and flaws appear at certain rates based on design and testing of the code. Verification of code quality can be improved by the application of greater resources and techniques but is expensive.

#### Suggested solutions:

- Reduce the size of the code base

- Isolate the security critical code into a small code base for concentrated analysis

- Invite independent analysis

- Deploy development regimes (coding standards and documentation methodologies) that lead to best practice

- Provide execution environments that guard against flawed code by restricting the developer (reduced instruction set, controlled data import and export options)

| T.SWO.007 Unpredictable CPU | Hard | Easy | WWW |

|-----------------------------|------|------|-----|

| instructions                |      |      |     |

|                             |      |      |     |

#### Description:

On a 32 bit RISC processor there are a potential  $2^{32}$  instructions (in real systems it is actually more than this but a sensible figure is 4 billion instructions). Not all of these are defined.

When an undefined instruction is executed the processor should perform an exception, but can potentially end up in an undefined state and therefore cause a security leak.

It is also possible for the processor, through error or external interference, to find itself in a state that should not be reachable. For example: receiving security data into a register that has changed to a non-secure mode between the time the data request was made, and the time the actual data reaches the register.

#### Suggested Solutions:

• Do not use native code, where a Threat Agent may introduce such

Page 26 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

#### undefined instructions

Use a processor where all native instruction options (including undefined) are verified in the RTL as being incapable of illegally breaking the secure execution boundary

| T.SWO.008 DMA or CLCD use | Moderate | Easy | WWW |

|---------------------------|----------|------|-----|

| for accessing memories    |          |      |     |

|                           |          |      |     |

#### Description:

DMA (Direct Memory Access) is a method used to move data in the device independently of the CPU. As such it is not blocked by MMU level defences and the user/privileged split.

Such properties are typical also for other hardware modules that have "bus master" rights, so a similar Attack might be achieved via other "bus masters" such as another CPU, a CLCD controller, an ethernet controller, or even a camera block.

#### Suggested Solutions:

- Place access to the DMA system behind trustable software

- Restrict the memory the DMA system can access with hardware extensions (address space limiters, microprogrammable DMA, MMU platform extensions, etc.) so that DMA cannot be used to move unauthorised data and hence steal secrets

| T.SWO.009 Faking of general | Moderate | Easy | WWW |

|-----------------------------|----------|------|-----|

| software identity           |          |      |     |

#### Description:

Typically general OS's have some way of uniquely identifying an application. When software makes use of a security API, the protection offered may be broken by fooling that API as to the identity of the calling application. An example of this is an API that only will release keys to application ID 325, so application ID 666 breaks other (weaker) security in the environment to claim to be 325.

#### Suggested solutions:

If the identity of an application is broken, then the general OS can be considered broken. The protection then is to only have exposed APIs that perform non-critical operations (i.e. don't have an operation for retrieving a key once placed behind a security boundary). This means that services that make use of the key also have to be placed behind the same security boundary.

Page 27 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

To enable this form of defence and yet perform required tasks, it must be possible for an application to move actual code behind the security boundary, without endangering that boundary for other users.

| T.SWO.010 CLCD use for          | Moderate | Easy | WWW |

|---------------------------------|----------|------|-----|

| displaying memories and         |          |      |     |

| interfering with displayed data |          |      |     |

|                                 |          |      |     |

#### Description:

This is a Threat similar to T.SWO.008. It is however separate because the information generated is immediately available outside the device, and so does not require so much in the way of supporting software.

The CLCD (Colour LCD) controller is the graphics chip in a mobile device. CLCD controllers are designed to be pointed at memory blocks which normally contain graphics data. This usually bypasses the CPU's MMU and any privileged / user protections it may offer.

For games, graphics chips typically have to be pointed at different memory banks by the game code. If no hardware protection exists then a 'game' can be used to display secrets on the screen. Interpreting the screen may be difficult as it is just 'raw' memory, but it is possible. It can be considered relatively easy Attack to perform, as graphics processors tend to allow this sort of capability through programmer-friendly APIs. However the translation of the data may be considered more difficult as a moderate knowledge of graphic display formatting is required.

#### Suggested Solutions:

- Use hardware means to block access from CLCD device to critical secrets

- Place Access Control software between the CLCD and applications to restrict target memory

| T.SWO.011 Attack through    | Moderate | Easy | WWW |

|-----------------------------|----------|------|-----|

| uncontrolled API in general |          | -    |     |

| software space              |          |      |     |

| _                           |          |      |     |

#### **Description:**

By uncontrolled, we are referring to APIs that are not designed from a security point of view. While they may be Type-Safe or Type-Unsafe, they should just be considered 'untrusted' if they have the potential to breach the security domain.

© 2009 OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 28 of 50 OMTP PUBLISHED

# **Suggested Solutions:**

Separate security and general API domains

#### **Description:**

If a program can issue commands to do anything, e.g. access any memory, then it is difficult to protect secrets from such a program. In a typical system, the user/privileged code split restricts the actual instructions available to user space native code, as well as the memory it can access. For example; user space native code cannot issue commands to switch off the user/privileged space separation.

This threat is realised by user space code breaking into the privileged space by some means, such as a Buffer Overflow attack.

### Suggested Solutions:

In any security code environment it is desirable to heavily control the functionality a programmer has to a limited set of instructions that are considered security safe

| T.SWO.013 Attack through     | Hard | Moderate | WWW |

|------------------------------|------|----------|-----|

| interaction of software      |      |          |     |

| concurrent processes causing |      |          |     |

| logical breaks               |      |          |     |

#### Description:

Malicious software could exploit scheduling concurrence to let a task access another task resources (e.g. where an operating system dynamically schedules processes that use common resources, by exploiting a race condition). This security problem is described in T.SWO.013. <u>Suggested</u> Solutions:

- Avoid any concurrence (i.e. with a single thread model)

- Stay with a simple thread interaction model in any area that is dealing with security, and isolate that area cleanly from other more complex processing models

- If using multi-threaded model, use an approach that allows the demonstration of robustness against the above threat.

Page 29 of 50 OMTP PUBLISHED

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

| T.SWO.014 Exploit software bugs in execution environment | Moderate | Easy | WWW |

|----------------------------------------------------------|----------|------|-----|

| Descriptions                                             |          |      |     |

Any software environment has the potential for bugs.

# **Suggested Solutions:**

- Reduce the amount of code that can potentially access the environment containing the security critical code

- Perform more validation and quality control effort on the security code compared to normal code environments

- Get external validation of the code

- Use developers who are aware of security and quality development issues. Special consideration should be given to selecting and training such developers, as in many instances prior experience may have conditioned them to produce rich, rather than secure, code

| T.SWO.015 Software Attack on | Moderate | Easy | WWW |

|------------------------------|----------|------|-----|

| Type Unsafe APIs inside the  |          | -    |     |

| execution environment        |          |      |     |

|                              |          |      |     |

## **Description:**

The Threat is that even if the boundary between secure and non-secure environments is protected by Type-Safe APIs, that if there are Type-Unsafe APIs in the secure environment then these may cause security holes. Typically we are looking at limiting damage from bugs rather than hackers operating inside the security environment, though that should not be discounted completely.

#### Suggested solution:

Make use of Type-Safe APIs when possible inside a security environment. The in-built structural checking of the command data tends to reduce any effects of erroneous events

| T.SWO.016 Software Attack on | Hard | Easy | WWW |

|------------------------------|------|------|-----|

| Type-Safe APIs inside the    |      | -    |     |

| Execution Environment        |      |      |     |

<sup>© 2009</sup> OMTP Limited. All rights reserved. No part of this document may be reproduced or transmitted in any form or by any means without prior written permission from OMTP Limited.

Page 30 of 50 OMTP PUBLISHED

The Threat is that even with Type-Safe APIs we may still see internal actions that are undesirable. In that case security should be guarded by consideration of what those Type-Safe APIs expose. For example, does the secure cryptography API have to work with keys, or can it work with handles to those keys, and leave the keys in secure storage.

# **Suggested Solutions:**

Design internal APIs to consider information hiding / access restriction wherever possible

| T.SWO.017 Attack Through | Moderate | Easy | WWW |

|--------------------------|----------|------|-----|

| Virtual Debug Port       |          |      |     |

|                          |          |      |     |

#### Description:

A debug port need not be implemented as a hardware interface, but could be exposed as a software mechanism. A malicious application could then use that port for any attacks that could be attempted on a physical port, but with the ability for the attack to be distributed easily and executed remotely.

#### **Suggested Solutions:**

- Provide authentication mechanisms for access to the port

- Add a hardware lock to prevent usage in the field

- Ensure that the debug port cannot access security critical assets

# 4.3 HARDWARE THREATS – EXTERNAL (T.HWE.XXX)

| THREAT DESCRIPTION                                                                               | REQUIRED  | EASE OF  | EASE OF      |

|--------------------------------------------------------------------------------------------------|-----------|----------|--------------|

|                                                                                                  | EXPERTISE | REPEAT   | DISTRIBUTION |

| T.HWE.001 Unauthorised access via external invasive or non-invasive debug ports (e.g. JTAG, ETM) | Moderate  | Moderate | Small Corp   |

## **Description:**

Security critical code and data may be held in memory. If that memory is accessible to the processor, then invasive or non-invasive debug ports can be used to extract that information. Invasive debug consists of a debug session that modifies or interrupts the program flow, such as the insertion of a breakpoint. Non-invasive debug does not alter program flow and is used to

Page 31 of 50 OMTP PUBLISHED